內容簡介

《專用集成電路低功耗入門:分析、技術和規範》重點關注CMOS數位專用集成電路(ASIC)設備,集中探討了三個主要內容:如何分析或量測功耗,如何為設備指定功耗意圖,以及可以用什麼科技最小化功耗。 《專用集成電路低功耗入門:分析、技術和規範》採用易於閱讀的風格編寫,章節間幾乎沒有依賴關係,讀者可以直接跳到感興趣的章節進行閱讀。 本書起始章節主要介紹如何量測功耗; 隨後的章節介紹低功耗的實現策略; 尤其在最後,還介紹了可用於描述功耗意圖的語言。

《專用集成電路低功耗入門:分析、技術和規範》適合從事晶片設計或具備邏輯設計背景的工程技術人員閱讀,也可作為高等院校集成電路科學與工程、電子科學與科技、微電子學與固體電子學等專業的高年級大學生和研究生的教材和參考書。

作者簡介

Rakesh Chadha是一名資深電腦輔助工程與設計專家,擁有逾25年的專業經驗,其中18年深耕於項目領導與科技管理領域。 他在Sematech項目中的晶片寄生效應選取和信號完整性驗證方面,首長時序和信號完整性工作。 他是eSilicon公司的設計技術總監,負責複雜的SOC設計方法學。

J. Bhasker是硬體描述語言和RTL綜合領域的著名專家。 他曾是兩個工作組(IEEE 1076.6 VHDL綜合工作組和IEEE 1364.1 Verilog綜合工作組)的主席,並於2005年獲得了IEEE電腦協會的傑出貢獻獎。 他是eSilicon公司的架構師,負責許多複雜設計的時序驗證工作。

目錄

前言

致謝

第1章引言1

1.1什麼是功耗1

1.2為什麼功耗很重要2

1.3為什麼功耗越來越大2

1.4功耗去哪了3

1.5多少才算低4

1.6為什麼要量測5

1.7對設計複雜度的影響6

1.8本書概要7

第2章覈心邏輯中的功耗建模8

2.1數位設計中的功耗8

2.1.1使用理想開關的例子8

2.1.2 CMOS數位邏輯10

2.2動態或活動功耗14

2.2.1組合單元的活動功耗14

2.2.2時序單元的活動功耗17

2.2.3內部功耗對參數的依賴19

2.3洩漏功耗20

2.3.1對閾值電壓的依賴20

2.3.2對溝道長度的依賴20

2.3.3對溫度的依賴21

2.3.4對工藝的依賴21

2.3.5洩漏功耗建模22

2.4高級功耗建模23

2.4.1洩漏電流23

2.4.2動態電流24

2.5總結25

第3章輸入輸出和宏模塊中的功耗建模27

3.1記憶體宏模塊27

3.1.1動態或活動功耗28

3.1.2洩漏功耗31

3.2類比宏模塊中的功耗33

3.3輸入輸出緩衝器的功耗34

3.3.1通用的數位輸入輸出模塊34

3.3.2帶終端的高速輸入輸出模塊40

3.4總結44

第4章ASIC中的功耗分析45

4.1什麼是開關活動性45

4.1.1靜態概率46

4.1.2翻轉率46

4.1.3實例46

4.2基本單元和宏模塊的功耗計算47

4.2.1 2輸入反及閘單元的功耗計算47

4.2.2觸發器單元的功耗計算53

4.2.3記憶體宏模塊的功耗計算56

4.3在模塊或晶片級指定活動性59

4.3.1默認全域活動性或非向量59

4.3.2通過輸入傳播活動性59

4.3.3 VCD 60

4.3.4 SAIF 62

4.4晶片級功耗分析65

4.4.1選擇PVT角65

4.4.2功耗分析65

4.5總結66

第5章電源管理的設計意圖68

5.1電源管理要求68

5.2電源域69

5.2.1電源域狀態70

5.3用於電源管理的特殊單元71

5.3.1隔離單元71

5.3.2電平移位器73

5.3.3使能電平移位器76

5.3.4電源開關77

5.3.5常開單元81

5.3.6保持單元83

5.3.7時鐘門控單元86

5.3.8標準單元90

5.3.9雙軌記憶體92

5.4總結93

第6章低功耗的架構科技94

6.1總體目標94

6.1.1影響功耗的參數95

6.2動態頻率96

6.3動態電壓縮放97

6.4動態電壓和頻率縮放98

6.5降低電源電壓98

6.6結構級時鐘門控99

6.7電源門控100

6.7.1狀態保持101

6.7.2粗細微性和細粒度電源門控102

6.8多電壓103

6.8.1優化電平移位器104

6.8.2優化隔離單元105

6.9優化記憶體功耗106

6.9.1對記憶體訪問進行分組106

6.9.2避免使能引脚上的冗餘活動108

6.10操作數隔離109

6.11設計的工作模式110

6.12 RTL科技110

6.12.1最小化翻轉次數111

6.12.2資源共亯111

6.12.3其他112

6.13總結112

第7章低功耗實現科技113

7.1工藝節點與庫的權衡113

7.2庫的選擇114

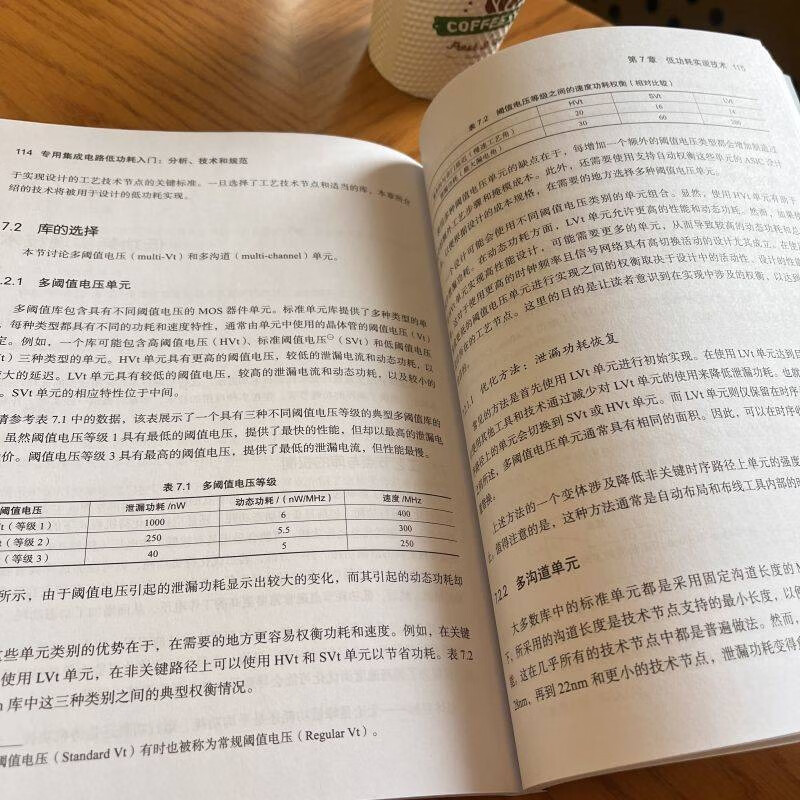

7.2.1多閾值電壓單元114

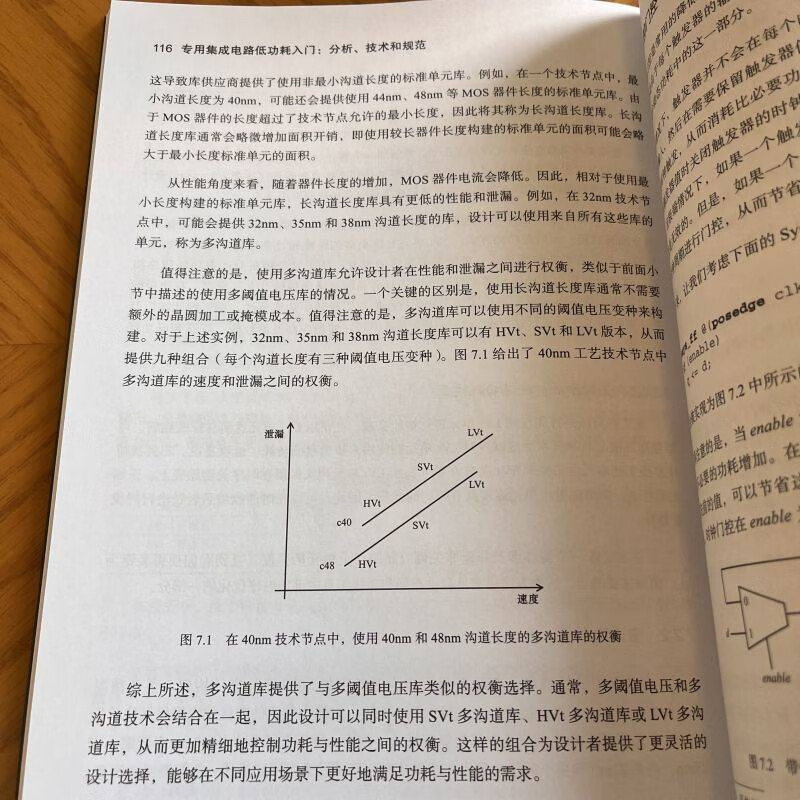

7.2.2多溝道單元115

7.3時鐘門控117

7.3.1功耗驅動的時鐘門控118

7.3.2降低時鐘樹功耗的其他科技119

7.4時鐘門控對時序的影響120

7.4.1單級時鐘門控120

7.4.2多級時鐘門控122

7.4.3尅隆時鐘門控123

7.4.4合併124

7.5門級功耗優化科技124

7.5.1使用複雜單元125

7.5.2調節單元尺寸125

7.5.3設定適當的壓擺率125

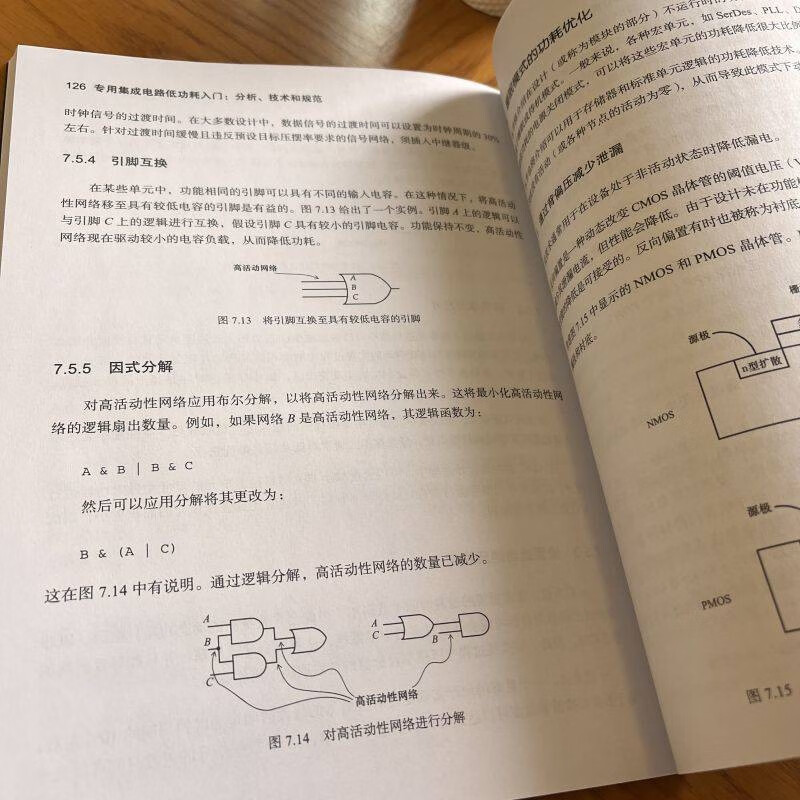

7.5.4引脚互換126

7.5.5因式分解126

7.6睡眠模式的功耗優化127

7.6.1通過背偏壓减少洩漏127

7.6.2關閉不活動的區塊128

7.6.3記憶體的睡眠和關機模式132

7.7自我調整工藝監控135

7.8去耦電容和洩漏136

7.9總結136

第8章UPF功耗規範137

8.1設定範圍138

8.2創建電源域138

8.3創建供電埠139

8.4創建供電網絡140

8.5連接供電網絡140

8.6域的主電源141

8.7創建電源開關141

8.8映射電源開關142

8.9供電埠的狀態142

8.10電源狀態錶143

8.11電平移位器規格144

8.12隔離策略146

8.13保持策略147

8.14映射保持寄存器148

8.15 Mychip實例149

第9章CPF功耗規範154

9.1簡介154

9.2庫命令155

9.2.1定義常開單元155

9.2.2定義全域單元155

9.2.3定義隔離單元156

9.2.4定義電平移位器單元156

9.2.5定義開放源極輸入引脚157

9.2.6定義焊盤單元157

9.2.7定義電源鉗比特單元158

9.2.8定義電源鉗比特引脚158

9.2.9定義電源開關單元158

9.2.10定義相關電源引脚159

9.2.11定義狀態保持單元160

9.3電源模式命令160

9.3.1創建模式160

9.3.2創建電源模式161

9.3.3指定電源模式轉換管道161

9.3.4設定電源模式控制組162

9.3.5結束電源模式控制組設定163

9.4設計和實現約束163

9.4.1創建分析視圖163

9.4.2創建偏壓網絡163

9.4.3創建全域連接164

9.4.4創建接地網絡164

9.4.5創建隔離規則164

9.4.6創建電平移位器規則165

9.4.7創建標稱條件165

9.4.8創建操作角166

9.4.9創建焊盤規則166

9.4.10創建電源域167

9.4.11創建電源網絡168

9.4.12創建電源開關規則168

9.4.13創建狀態保持規則169

9.4.14定義庫集合170

9.4.15標識常開驅動器170

9.4.16標識電源邏輯