![【NAND閃存科技】[日]有留誠一 【NAND閃存科技】[日]有留誠一](https://theorient.net/Public/Uploads/202504/67f501a533e0c.jpg)

![【NAND閃存科技】[日]有留誠一 【NAND閃存科技】[日]有留誠一](https://theorient.net/Public/Uploads/202504/67f501b58891e.jpg)

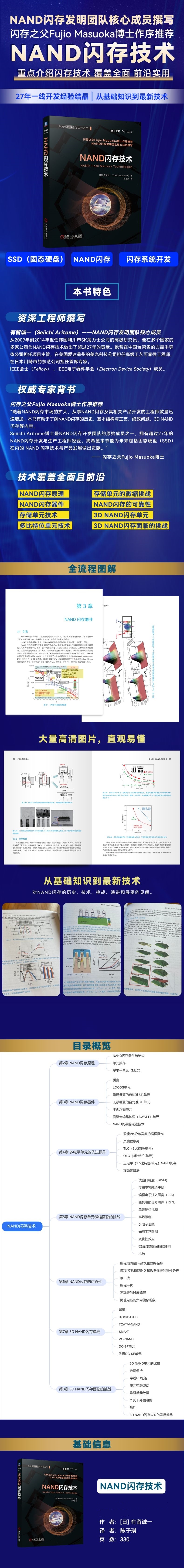

【NAND閃存科技】

編輯推薦

NAND閃存是電晶體非易失性記憶體,其應用十分廣泛,主要用於智能手機、固態硬碟(SSD)、資料中心等領域,並且在平板電腦、U盤、數位相機、MP3播放機、遊戲機、汽車電子等各種消費電子和嵌入式設備中也有廣泛應用,隨著人工智慧和DeepSeek等大模型的推動,對閃存的需求有望進一步爆發。 本書作者是NAND閃存發明團隊的核心成員,擁有超過27年的閃存開發經驗,並且本書還得到了閃存之父Fujio Masuoka博士親自作序推薦。 《NAND閃存技術》這本書討論了基本和先進的NAND閃存科技,包括NAND閃存的原理、存儲單元科技、多比特比特單元科技、存儲單元的微縮挑戰、可靠性和作為未來科技的3D單元。 《NAND閃存技術》這本書不僅把NAND閃存科技從開始出現到發展成熟的過程梳理得很清楚,還深入分析了底層原理、最新的科技突破,以及未來的發展趨勢。 不管是剛接觸NAND閃存科技的新手,還是在這個行業鑽研多年的資深人士,都能從這本書裏學到新知識,得到新啟發。

內容簡介

《NAND閃存技術》討論了基本和先進的NAND閃存科技,包括NAND閃存的原理、存儲單元科技、多比特比特單元科技、存儲單元的微縮挑戰、可靠性和作為未來科技的3D單元。 第1章描述了NAND閃存的背景和早期歷史。 第2章描述了器件的基本結構和操作。 接下來,第3章討論了以微縮為重點的存儲單元科技,並且第4章介紹了多電平存儲單元的先進操作。 第5章討論了微縮的物理限制。 第6章描述了NAND閃存的可靠性。 第7章研究了3D NAND閃存單元,並討論了結構、工藝、操作、可擴展性和效能方面的優缺點。 第8章討論了3D NAND閃存面臨的挑戰。 最後,第9章總結並描述了未來NAND閃存的科技和市場前景。

《NAND閃存技術》適合從事NAND閃存或SSD(固態硬碟)和閃存系統開發的工程師、研究人員和設計人員閱讀,也可供高等院校集成電路、微電子、電子技術等專業的師生參攷。

作者簡介

Seiichi Aritome從2009年到2014年擔任韓國利川市SK海力士公司的高級研究員。 他在多個國家的多家公司為NAND閃存科技做出了超過27年的貢獻。 他曾在中國臺灣省的力晶電晶體公司擔任項目首長,在美國愛達荷州的美光科技公司擔任高級工藝可靠性工程師,在日本川崎市的東芝公司擔任首席專家。 他畢業於日本廣島大學高等物質科學研究生院,獲博士學位。 他是IEEE會士(Fellow)和IEEE電子器件學會(Electron Device Society)的成員。

目錄

目錄

譯者序

原書序

原書前言

致謝

作者簡介

第1章引言1

1.1背景1

1.2概述6

參考文獻8

第2章NAND閃存原理14

2.1 NAND閃存器件與結構14

2.1.1 NAND閃存單元結構14

2.1.2週邊器件16

2.2單元操作17

2.2.1讀操作17

2.2.2程式設計和擦除操作18

2.2.3程式設計和擦除的動力學過程23

2.2.4程式設計升壓操作26

2.3多電平單元(MLC)28

2.3.1單元閾值電壓設定28

參考文獻29

第3章NAND閃存器件31

3.1引言31

3.2 LOCOS單元33

3.2.1常規LOCOS單元33

3.2.2先進LOCOS單元34

3.2.3隔離科技35

3.2.4可靠性38

3.3帶浮栅翼的自對準STI單元40

3.3.1自對準STI單元結構40

3.3.2製備工藝流程40

3.3.3帶浮栅翼的自對準STI單元的特性44

3.3.4週邊器件特性47

3.4無浮栅翼的自對準STI單元49

3.4.1自對準STI單元結構49

3.4.2製備工藝流程51

3.4.3 STI科技52

3.4.4自對準STI單元的特性53

3.5平面浮栅單元55

3.5.1結構優勢55

3.5.2電學特性56

3.6側壁傳輸電晶體(SWATT)單元58

3.6.1 SWATT單元概念58

3.6.2製備工藝60

3.6.3電學特性62

3.7 NAND閃存的先進科技65

3.7.1虛擬字線65

3.7.2 p型浮栅69

參考文獻75

第4章多電平單元的先進操作79

4.1引言79

4.2緊湊Vth分佈寬度的程式設計操作79

4.2.1單元Vth設定79

4.2.2增量步進脈衝程式設計(ISPP)81

4.2.3逐比特驗證操作83

4.2.4兩步驗證方案84

4.2.5頁程式設計中的偽通過方案86

4.3頁程式設計序列88

4.3.1原始頁程式設計方案88

4.3.2新的頁程式設計方案(一)90

4.3.3新的頁程式設計方案(二)92

4.3.4全比特線(ABL)架構93

4.4 TLC(3比特比特/單元)95

4.5 QLC(4比特比特/單元)99

4.6三電平(1.5比特比特/單元)NAND閃存101

4.7移動讀算灋103

參考文獻104

第5章NAND閃存單元微縮面臨的挑戰109

5.1引言109

5.2讀視窗裕度(RWM)110

5.2.1 RWM的假設條件110

5.2.2程式設計態Vth分佈寬度114

5.2.3 Vth視窗116

5.2.4 RWM118

5.2.5 RWM中Vth設定的依賴性118

5.3浮栅電容耦合干擾119

5.3.1浮栅電容耦合干擾模型120

5.3.2溝道直接耦合122

5.3.3源漏耦合124

5.3.4空氣隙和低k資料126

5.4程式設計電子注入展寬(EIS)129

5.4.1程式設計EIS理論129

5.4.2浮栅低摻雜效應133

5.5隨機電報訊號雜訊(RTN)136

5.5.1閃存單元中的RTN136

5.5.2 RTN的微縮趨勢139

5.6單元結構挑戰143

5.7高場限制144

5.8少電子現象147

5.9光刻工藝限制149

5.10變化性效應151

5.11微縮對數據保持的影響153

5.12小結155

參考文獻156

第6章NAND閃存的可靠性163

6.1引言163

6.2程式設計/擦除迴圈耐久和數據保持165

6.2.1程式設計/擦除方案165

6.2.2程式設計/擦除迴圈耐久167

6.2.3數據保持特性169

6.3程式設計/擦除迴圈耐久和數據保持的特性分析175

6.3.1程式設計/擦除迴圈退化175

6.3.2應力誘導漏電流(SILC)180

6.3.3 NAND閃存產品中的數據保持183

6.3.4分布式迴圈測試185

6.4讀干擾187

6.4.1程式設計/擦除方案的依賴性187

6.4.2脫阱和SILC191

6.4.3 NAND閃存產品中的讀干擾194

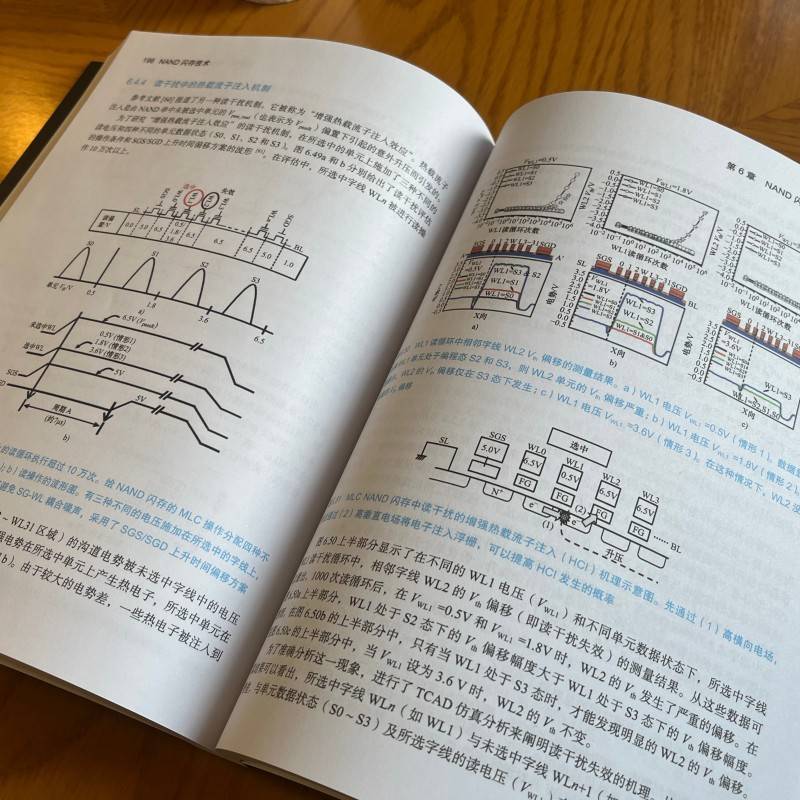

6.4.4讀干擾中的熱載流子注入機制196

6.5程式設計干擾198

6.5.1自升壓模型198

6.5.2熱載流子注入機制202

6.5.3溝道耦合206

6.6不穩定的過度程式設計208

6.7閾值電壓的負向偏移現象211

6.7.1背景和實驗211

6.7.2閾值電壓負向偏移212

6.7.3程式設計速度和受害單元的閾值電壓依賴性213

6.7.4程式設計條件下的載流子分離217

6.7.5模型219

6.8小結220

參考文獻222

第7章3D NAND閃存單元229

7.1背景229

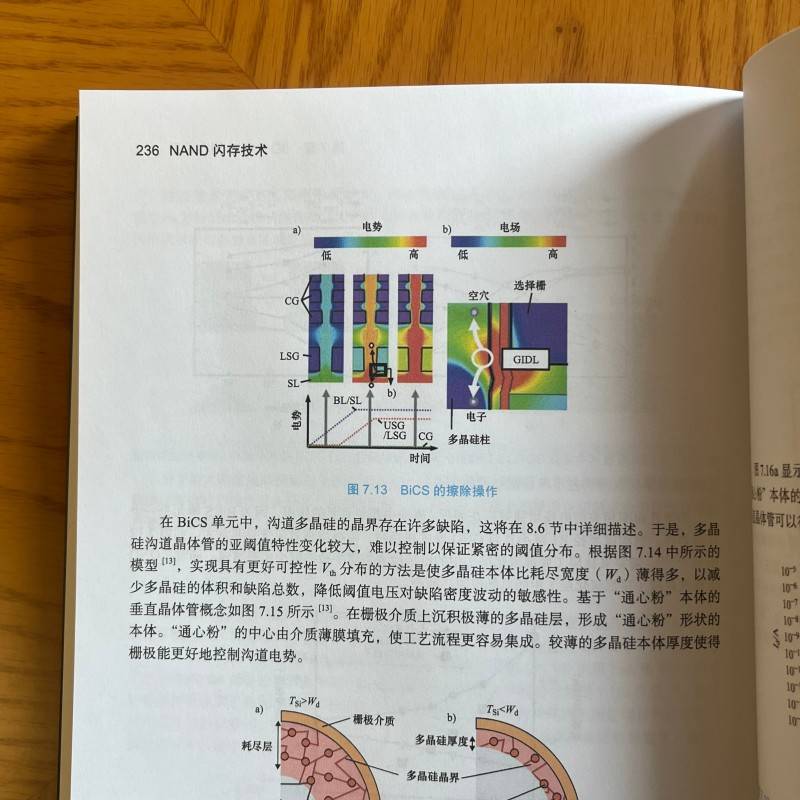

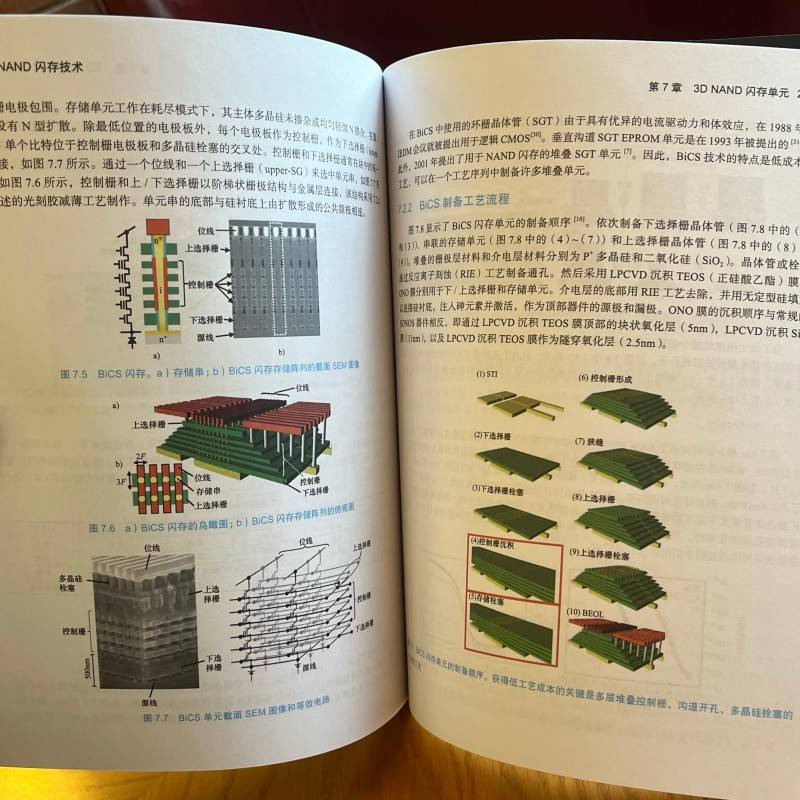

7.2 BiCS/P-BiCS231

7.2.1 BiCS的概念231

7.2.2 BiCS製備工藝流程233

7.2.3電學特性234

7.2.4管形BiCS239

7.3 TCAT/V-NAND243

7.3.1 TCAT結構和製備工藝流程243

7.3.2電學特性246

7.3.3 128Gbit MLC NAND閃存247

7.3.4 128Gbit TLC V-NAND閃存249

7.4 SMArT251

7.4.1 SMArT結構的先進性251

7.4.2電學特性253

7.5 VG-NAND254

7.5.1 VG-NAND的結構和製備工藝流程254

7.5.2電學特性256

7.6 DC-SF單元259

7.6.1電荷陷阱型3D單元的問題259

7.6.2 DC-SF NAND閃存單元259

7.6.3結果和討論264

7.6.4微縮能力266

7.7先進DC-SF單元267

7.7.1 DC-SF單元上的改進267

7.7.2 MCGL工藝268

7.7.3新的讀方案268

7.7.4新的程式設計方案274

7.7.5可靠性276

參考文獻277

第8章3D NAND閃存面臨的挑戰282

8.1引言282

8.2 3D NAND單元的比較283

8.3數據保持286

8.3.1快速初始電荷損失286

8.3.2溫度依賴性288

8.4程式設計干擾289

8.4.1新的程式設計干擾模式289

8.4.2程式設計干擾的分析290

8.5字線RC延遲295

8.6單元電路波動297

8.6.1傳導機理297

8.6.2 VG依賴性301

8.6.3 RTN303

8.6.4“通心粉”溝道的背端陷阱305

8.6.5雷射熱退火309

8.7堆疊單元數量310

8.8陣列下週邊電路312

8.9功耗314

8.10 3D NA...

-----------------------------------------------------------------

【電晶體存儲器件與電路】

內容簡介

《半導體存儲器件與電路》對半導體記憶體科技進行了全面綜合的介紹,覆蓋了從底層的器件及單元結構到頂層的陣列設計,且重點介紹了近些年的工藝節點縮小趨勢和最前沿的科技。 本書第1部分討論了主流的半導體記憶體科技,第2部分討論了多種新型的記憶體科技,這些科技都有潜力能够改變現有的存儲層級,同時也介紹了記憶體科技在機器學習或深度學習中的新型應用。

《半導體存儲器件與電路》可作為高等院校微電子學與固體電子學、電子科學與科技、集成電路科學與工程等專業的高年級大學生和研究生的教材和參考書,也可供電晶體和微電子領域的從業人員參攷。

作者簡介

餘詩孟是佐治亞理工學院電子與電腦工程系教授,也是IEEE會士(Fellow)。 餘教授的研究興趣包括用於高能效計算系統的半導體器件和集成電路。 他的研究專長主要是新型非易失性存儲技術及相關應用,包括在深度學習加速器、存算一體、3D集成和硬體安全等多方面的應用。 他已發表了400多篇經同行評審的會議和期刊論文,並擁有超過30000次的Google Scholar引用,H因數為82。

目錄

譯者序

前言

致謝

作者簡介

第1章半導體記憶體科技概述

1.1記憶體層次結構介紹

1.1.1澤級數據爆炸

1.1.2存儲子系統中的記憶體層次結構

1.2半導體記憶體產業

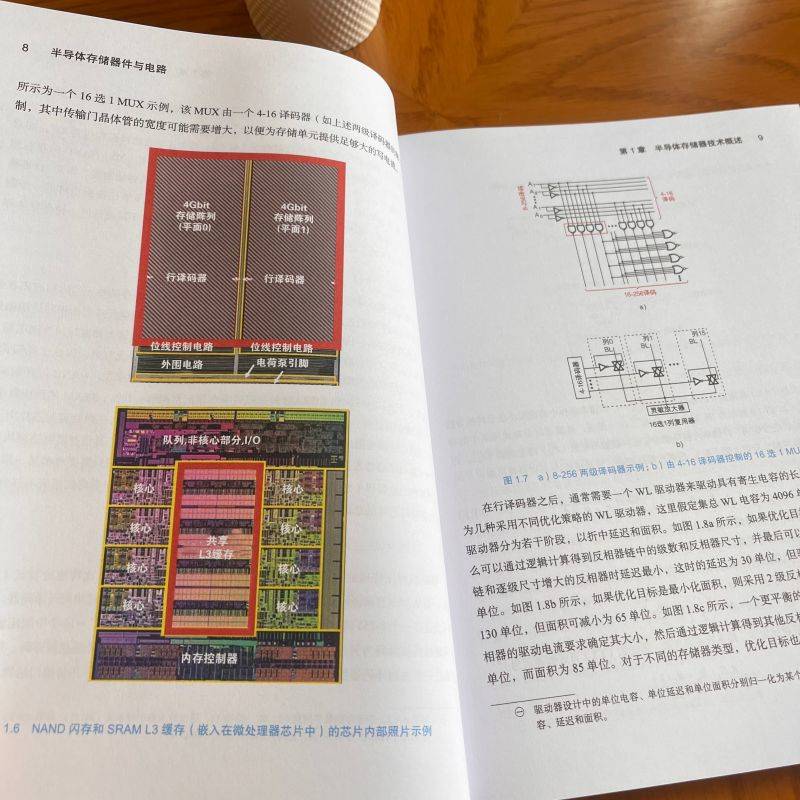

1.3存儲陣列結構介紹

1.3.1通用存儲陣列結構圖

1.3.2存儲單元尺寸和等效比特面積

1.3.3存儲陣列的面積效率

1.3.4週邊電路:解碼器、多工器和驅動器

1.3.5週邊電路:靈敏放大器

1.4工業界的科技發展趨勢

1.4.1摩爾定律與邏輯電路微縮趨勢

1.4.2工藝節點的定義和集成密度的量測標準

1.5邏輯電晶體的工藝演變

參考文獻

第2章靜態隨機存取記憶體(SRAM)

2.1 6T SRAM單元操作

2.1.1 SRAM陣列和6T單元

2.1.2保持、讀取和寫入的原理

2.2 SRAM穩定性分析

2.2.1靜態雜訊容限

2.2.2 N曲線

2.2.3動態雜訊容限

2.2.4讀與寫的輔助方案

2.3 SRAM的漏電流

2.3.1電晶體的亞閾值電流

2.3.2降低SRAM的漏電流

2.4漲落和可靠性

2.4.1電晶體本征參數波動及其對SRAM穩定性的影響

2.4.2時變可靠性問題及其對SRAM穩定性的影響

2.4.3輻射效應造成的軟錯誤

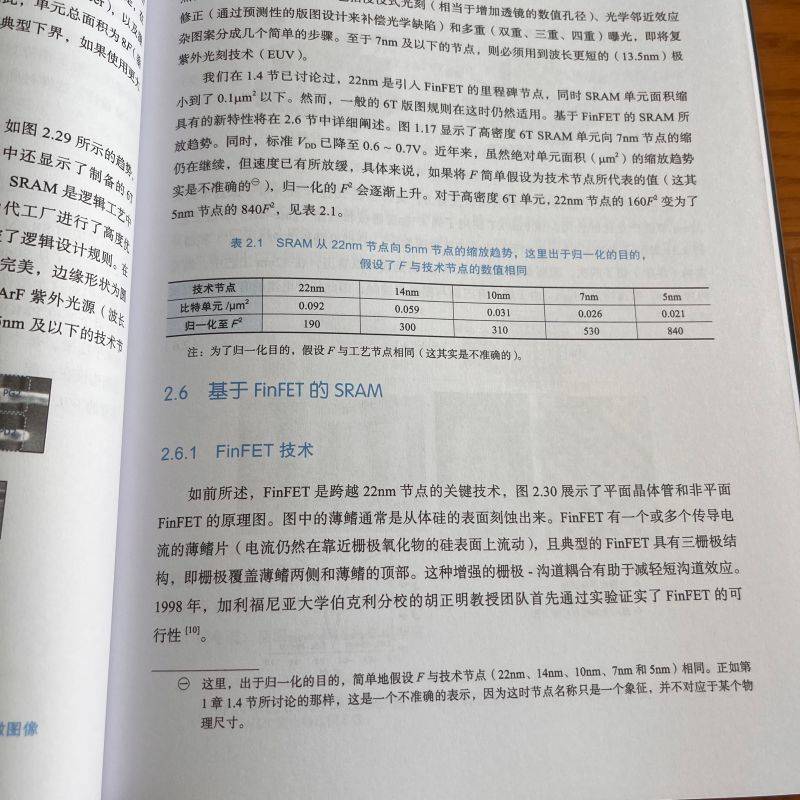

2.5 SRAM版圖和微縮趨勢

2.5.1 6T單元版圖

2.5.2 SRAM微縮趨勢

2.6基於FinFET的SRAM

2.6.1 FinFET科技

2.6.2 FinFET時代SRAM的微縮

參考文獻

第3章動態隨機存取記憶體(DRAM)

3.1 DRAM概述

3.1.1 DRAM子系統層次結構

3.1.2 DRAM I/O介面

3.2 1T1C DRAM單元操作

3.2.1 1T1C單元的工作原理

3.2.2電荷共亯和感應

3.2.3 DRAM的漏電流與重繪

3.3 DRAM工藝

3.3.1溝槽電容和堆疊電容

3.3.2 DRAM陣列結構

3.3.3 DRAM版圖

3.4 DRAM微縮趨勢

3.4.1微縮挑戰

3.4.2單元電容

3.4.3互連線

3.4.4單元選通電晶體

3.5 3D堆疊DRAM

3.5.1 TSV科技與異構集成

3.5.2高頻寬記憶體(HBM)

3.6嵌入式DRAM

3.6.1 1T1C嵌入式DRAM

3.6.2無電容嵌入式DRAM

參考文獻

第4章閃存(Flash)

4.1 Flash概述

4.1.1 Flash的歷史

4.1.2 Flash的應用場景

4.2 Flash的器件原理

4.2.1浮栅電晶體的工作原理

4.2.2浮栅電晶體的電容模型

4.2.3浮栅電晶體的擦寫機制

4.2.4嵌入式Flash的源端注入

4.3 Flash的陣列結構

4.3.1 NOR陣列

4.3.2 NAND陣列

4.3.3 Flash陣列的週邊高壓電路

4.3.4 NAND Flash的編譯器

4.3.5 NOR和NAND的對比

4.4多比特Flash單元

4.4.1多比特Flash單元的基本原理

4.4.2增量步進脈衝程式設計(ISPP)

4.5 Flash的可靠性

4.5.1 Flash的擦寫壽命

4.5.2 Flash的保持特性

4.5.3 Flash的單元干擾

4.5.4可靠性問題之間的折中

4.6 Flash微縮的挑戰

4.6.1單元間串擾

4.6.2電子數量減少問題

4.7 3D NAND Flash

4.7.1電荷俘獲型電晶體的工作原理

4.7.2低成本的3D集成方法

4.7.3 3D NAND製造中的問題

4.7.4第一代3D NAND晶片

4.7.5 3D NAND的最新發展趨勢

參考文獻

第5章新型非易失性記憶體

5.1新型非易失性記憶體概述

5.1.1新型非易失性記憶體總覽

5.1.2 1T1R陣列

5.1.3交叉陣列和選通器

5.2相變記憶體(PCM)

5.2.1 PCM器件機理

5.2.2 PCM的可靠性

5.2.3 PCM陣列集成

5.2.4 3D X-point

5.3阻變隨機存取記憶體(RRAM)

5.3.1 RRAM器件機理

5.3.2 RRAM的可靠性

5.3.3 RRAM陣列集成

5.4磁性隨機存取記憶體(MRAM)

5.4.1 MTJ器件機理

5.4.2場轉變MRAM

5.4.3 STT-MRAM

5.4.4 SOT-MRAM

5.5鐵電記憶體

5.5.1鐵電器件機理

5.5.2 1T1C FeRAM

5.5.3 FeFET

5.6存算一體(CIM)

5.6.1 CIM原理

5.6.2突觸器件内容

5.6.3 CIM原型晶片

參考文獻

附錄名詞對照表

NT$1499

【DeepSeek高效使用秘笈:藍寶書+紅寶書】(套裝3册)

NT$1499

【低空無人機集羣科技】

NT$1600

【動力電池熱管理科技及關鍵資料】

NT$1850

【光刻膠資料評測科技】(從酚醛樹脂光刻膠到最新的EUV光刻膠)

NT$2150

無人機系統成像與感知:【控制與效能+部署與應用】

NT$1799

【超大規模集成電路物理設計:從圖分割到時序收斂】+【專用集成電路低功耗入門:分析、科技和規範】

NT$1799

【電晶體幹法刻蝕科技】

NT$1399

【車規級晶片科技】

NT$2750

【電晶體幹法刻蝕科技:原子層工藝】

NT$1999

【質子交換膜燃料電池基礎與效能計算】+【質子交換膜燃料電池混合動力、故障診斷和預測】

NT$1800

【MEMS三維晶片集成科技】+【電晶體先進光刻理論與科技】

NT$3300

集成電路系列:【矽通孔三維封裝技術】+【功率電晶體封裝技術】+【集成電路先進封裝資料】+【集成電路系統級封裝】

NT$2700

電子工程師:【元器件應用寶典】+【九大系統電路識圖寶典】+【電路板技能速成寶典】

NT$3000

新概念類比電路:【電晶體、運放和負反饋+頻率特性和濾波器+信號處理和源電路】

NT$3300

美國機械工程手冊第29版:【基礎卷】+【零部件卷】(套裝兩册,質重4公斤)

NT$2250

【納米集成電路FinFET器件物理與模型】+【氮化鎵功率晶體管 器件、電路與應用】+【半導體工程導論】

NT$2680

【CMOS集成電路EDA科技】+【CMOS類比集成電路版圖設計:基礎、方法與驗證】+【集成功率器件設計及TCAD模擬】+【用於集成電路模擬和設計的FinFET建模基於BSIM-CMG標準】

NT$3150

【功率半導體器件封裝技術】+【氮化鎵功率器件資料、應用及可靠性】+【晶片設計CMOS類比集成電路版圖設計與驗證】+【晶片製造電晶體工藝與設備】

NT$2350

【功率電晶體基礎與工藝精講(第2版)】+【電晶體製造設備基礎與構造精講(第3版)】+【電晶體制造技術基礎精講(第4版)】

NT$2500

【繞射極限附近的光刻工藝】+【計算光刻與版圖優化】+【雷射熱敏光刻:原理與方法】